-

OnePlus Pad Go 2 Surfaces on Geekbench, Tipping Dimensity 7300 and a 2.8K Display

The next-generation OnePlus Pad Go 2 has surfaced on Geekbench, hinting at significant upgrades with the MediaTek Dimensity 7300 chipset and a large 2.8K display.

-

OnePlus Ace 6T Review: A 165Hz Gaming Beast with an Unbelievable 8300mAh Battery

The OnePlus Ace 6T redefines gaming phones, pairing the new 5th Gen Snapdragon 8 with a stunning 165Hz display and an unprecedented 8300mAh battery for ultimate performance.

-

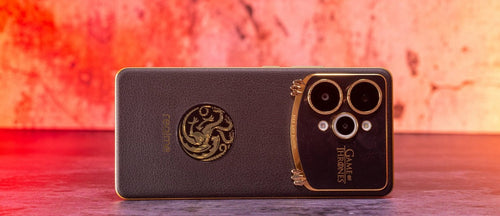

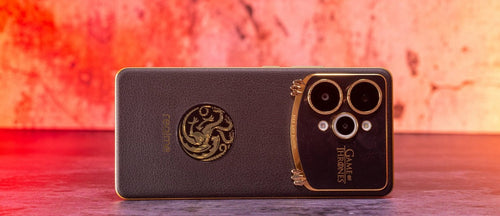

Realme Unveils 'Game of Thrones' GT5 Pro Edition with World-First Heat-Sensitive Color-Changing Design

Realme is launching a 'Game of Thrones' themed GT5 Pro on December 8, featuring a groundbreaking heat-sensitive design that changes color, a world-first for smartphones.

-

Sony Revives Its Classic Kit Lens: Introducing the FE 28-70mm F3.5-5.6 OSS II

Sony quietly launches the FE 28-70mm F3.5-5.6 OSS II, a long-overdue update to its original full-frame kit lens, bringing modern features to a versatile classic.

-

Motorola and Bose Team Up for "Soundflow" Smart Speaker, a Potential Smart Home Hub

Motorola and Bose are reportedly teaming up to launch the Soundflow, a new smart speaker designed to serve as a stylish and functional smart home hub.

-

Nubia Unveils the Flip 3: The Brand's Lightest Foldable with a Massive 4-Inch Cover Screen

Nubia introduces the Flip 3, its lightest foldable phone ever. Boasting a large 4-inch cover screen and a 6.9-inch main display, it redefines the compact foldable experience.

-

OnePlus x Genshin Impact: Get a Free Kamisato Ayaka Engraving on the Ace 2 Pro

OnePlus offers a limited-time, free engraving of Genshin Impact's Kamisato Ayaka on its Ace 2 Pro, alongside a new Paimon-themed gift box.

-

Samsung Galaxy S26 Ultra Rumored to Feature Four Color Options, with Purple as the Hero Shade

New rumors indicate the Samsung Galaxy S26 Ultra will arrive in four colorways, with a distinct purple shade expected to be the signature option for the new flagship.

-

Honor Magic5 Series Gets Major Gaming Boost with Phantom Frame Stabilization Update

The Honor Magic5 series is receiving a major gaming upgrade with the new Phantom Frame Stabilization feature, enhancing performance in 12 popular titles including Genshin Impact.

-

OnePlus Ace 6T Official Accessories Unveiled, Embracing the OPPO Mag Ecosystem

OnePlus has officially announced its new accessory lineup for the upcoming Ace 6T, featuring seamless integration with the OPPO Mag magnetic ecosystem for enhanced functionality and convenience.

-

Motorola Rumored to Launch Dazzling Swarovski Crystal Edge 70 with Pantone's 2026 Color of the Year

Motorola is rumored to release a stunning Swarovski Crystal Edition of the Edge 70, featuring Pantone's 2026 Color of the Year. A perfect blend of technology and luxury awaits.

-

Samsung Galaxy S26 Wallpapers Leak, Revealing Mint Green, Coral Orange, and More

Leaked default wallpapers for the upcoming Samsung Galaxy S26 series reveal a stunning new color palette, hinting at the design and color options for the new flagship phones.

-

Sony Alpha 7 V Design Revealed: Full-Frame Mirrorless Camera Tipped for December 2nd Launch

Images of the new Sony Alpha 7 V have surfaced, revealing the design of the next-gen full-frame camera ahead of its rumored December 2nd launch.

-

Vivo S50 Pro Mini Rear Design Unveiled: Horizontal Camera and 6.31-Inch Compact Screen Confirmed

The rear design of the upcoming vivo S50 Pro mini has been revealed, confirming a distinctive horizontal camera module and a compact 6.31-inch flat screen for the new device.

-

Explore the Depths: Huawei WATCH Ultimate 2 Launches with Sonar Messaging and Onboard AI

Huawei's new WATCH Ultimate 2 is now on sale, featuring groundbreaking dolphin sonar communication for divers, a built-in AI assistant, and premium materials for ultimate exploration.

-

Huawei Unveils Luxurious "Purple Gold" Edition of its WATCH ULTIMATE DESIGN

Huawei introduces the luxurious WATCH ULTIMATE DESIGN in a new "Purple Gold" colorway, combining premium craftsmanship with cutting-edge technology, now available for 24,999 Yuan.

-

Sony Unveils LYTIA 901: A 200MP Sensor Powerhouse for Next-Gen Flagship Phones

Sony has launched its new flagship mobile image sensor, the LYTIA 901, boasting a 200MP resolution, a large 1/1.12-inch format, and support for 4x single-camera zoom.

-

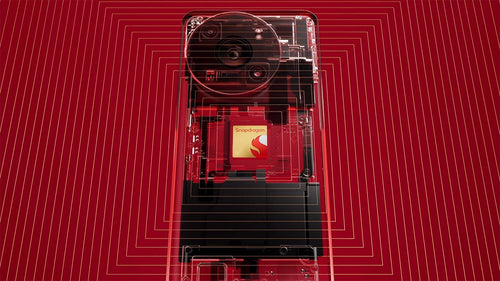

Snapdragon 8 Gen 6 Rumors: TSMC 2nm Process and Oryon Cores Tipped for Mid-Range Flagships

New rumors for the Snapdragon 8 Gen 6 point to a TSMC 2nm process, custom Oryon CPU cores, and a surprising new target market in the upper-mid-range smartphone segment.

-

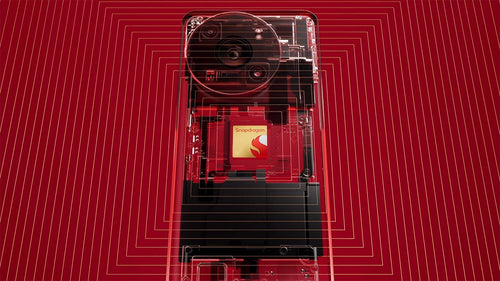

OnePlus Ace 6T Set for December 3 Debut, First to Feature Snapdragon 8 Gen 4

The OnePlus Ace 6T is set for a December 3 launch, confirmed to be the world's first smartphone to feature the powerful new Snapdragon 8 Gen 4 chipset.

-

Samsung's Next-Gen Odyssey OLED G6 Monitor Leaked: A 27-Inch 2K Display Eyeing a 2026 Launch

Samsung is reportedly developing a new 27-inch 2K QD-OLED gaming monitor, the Odyssey OLED G6, with a potential launch slated for CES 2026 and more affordable pricing.

-

Claude Opus 4.5 Arrives: Crushing Coding Tests and Heralding the 'Superman' Era of AI Programming

Anthropic's new Claude Opus 4.5 model redefines AI programming with record-breaking performance, enhanced tool integration, and superior efficiency, marking a new era for developers.

-

From CES Star to Financial Struggle: What Went Wrong with the Rabbit r1?

Once hailed as an AI pioneer, the Rabbit r1 now faces financial collapse. This is the story of its ambitious rise and precipitous fall.

-

iOS 27 Leaks: A Year of Refinements as Apple Prepares Its Big AI Comeback

Early reports on iOS 27 point to a year of refinement and bug fixes, with Apple's major AI advancements, including a new Siri, slated for a later release.

-

Chromebooks Level Up: Google and NVIDIA Launch GeForce NOW Fast Pass for Cloud Gaming

Chromebook users can now enjoy over 2000 PC games with the new NVIDIA GeForce NOW Fast Pass subscription, featuring no ads and no waiting.

-

Sony Alpha 7 V Rumors: Pre-Capture and 30fps RAW Shooting Tipped, But No Global Shutter

New reports suggest the upcoming Sony Alpha 7 V will feature pre-capture and 30fps 14-bit RAW shooting, though it is not expected to have a global shutter.

-

Dell Unveils Pro Max 16 Plus: The First Mobile Workstation with an Enterprise-Grade Dedicated NPU

Dell has announced the Pro Max 16 Plus, the first mobile workstation featuring an enterprise-grade dedicated NPU from Qualcomm for powerful, on-device AI processing.

-

Apple Watch Users Criticize watchOS 26 Workout App for Poor Usability

Following the release of watchOS 26, many Apple Watch users are criticizing the redesigned Workout app for its poor usability, citing smaller buttons and a more complex interface.

-

Leica Q3 Monochrom Leaked: 60MP Black & White Sensor, Premium Price Tag

Leica is rumored to launch the Q3 Monochrom, a premium full-frame camera featuring a dedicated 60MP black and white sensor for the ultimate in monochrome photography.

-

Vivo X Fold6 Rumored to Target Mainstream Market, Tests Next-Gen Snapdragon 8 Gen 5 Chip

New reports claim the vivo X Fold6 is taking a mainstream approach and is currently being tested with the advanced Snapdragon 8 Gen 5 processor.

-

Bowers & Wilkins Unveils Px8S2 McLaren Edition Headphones with Signature Papaya Orange Finish

Discover the new Bowers & Wilkins Px8S2 McLaren Edition headphones. This special collaboration features a signature Papaya Orange design, Nappa leather, and is priced at 7799 Yuan.

-

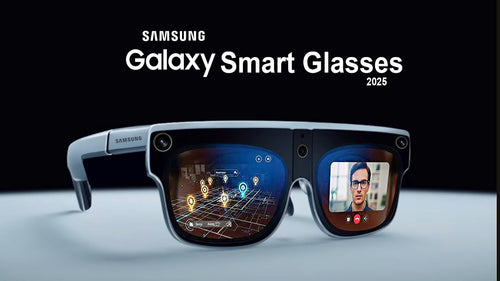

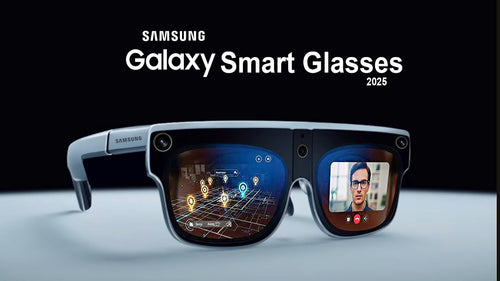

Samsung Reportedly Developing Two Smart Glasses, First Model with Photochromic Lenses Expected in 2026

Samsung is reportedly developing two smart glasses, with the first model launching in 2026. It will feature photochromic lenses and AI capabilities, but no AR display.

-

OnePlus Ace 6T Confirmed to Feature Top-Tier IP69K Water Resistance and 3D Ultrasonic Fingerprint Sensor

The OnePlus Ace 6T will feature class-leading IP69K water resistance and a standard 3D ultrasonic fingerprint scanner, promising superior durability and advanced biometric security.

-

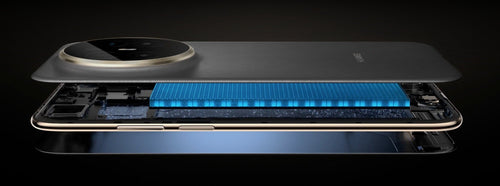

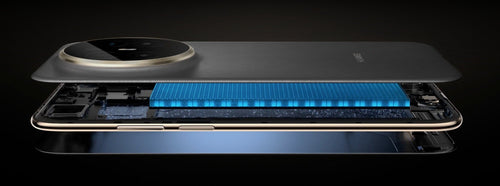

First Look: Hands-On with the Huawei MatePad Edge, the Premier HarmonyOS 2-in-1 Tablet

A hands-on review of the new Huawei MatePad Edge, the first 2-in-1 tablet running HarmonyOS. We explore the top-spec, liquid-cooled version unveiled on November 19.

-

Honor Watch X5 Set for November 24 Launch, Highlighting a Massive 1.97-inch AMOLED Display

Honor is set to release the Honor Watch X5 on November 24th, a new smartwatch featuring a massive 1.97-inch AMOLED display and an ultra-narrow 1.8mm bezel design.

-

Honor 500 Series Confirmed with Massive 8000mAh Batteries, Launch Set for Nov 24

Honor confirms its upcoming 500 series will feature 8000mAh batteries across all models. The new phones are set to launch on November 24th with flagship specifications.

-

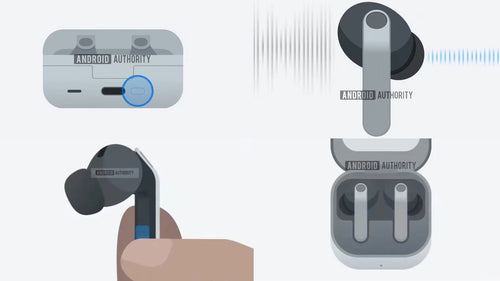

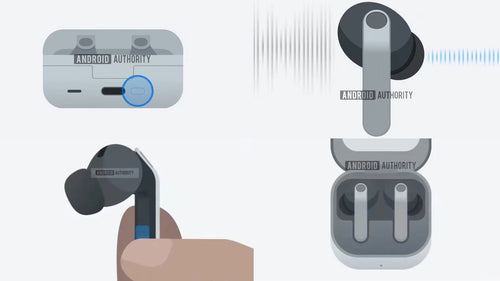

Samsung Galaxy Buds 4 Pro Leaks Reveal Major Redesign and Innovative Head Gesture Controls

Leaks reveal the Samsung Galaxy Buds 4 Pro, set for an early 2026 launch, will feature a major design overhaul and innovative hands-free head gesture controls.

-

Huawei FreeBuds Pro 5 Set for November 25 Launch with NearLink and Master-Level Lossless Audio

Huawei will unveil its FreeBuds Pro 5 YueZhang TWS earbuds on November 25, boasting NearLink connectivity, a Kirin A3 chip, and master-level lossless sound quality.

-

Vivo S50 Series Rumored to Feature Snapdragon 8 Gen 5, Compact 6.3-inch Display, and a Massive 6500mAh Battery

A rumored vivo S50 series smartphone is set to combine flagship power with incredible battery life, featuring a Snapdragon 8 Gen 5 chip and a massive 6500mAh battery.

-

Microsoft's Future Surface Trackpad 'Listens' to Itself for Auto-Calibration, Challenging Apple's Force Touch

Microsoft's new 'haptic-sonic' trackpad patent reveals a system that listens to its own clicks to auto-calibrate feel and ensure consistent feedback, challenging Apple's Force Touch.

-

Apple Releases watchOS 26.2 Developer Preview Beta 3

Apple seeds the third developer beta of watchOS 26.2, build 23S5297b. The update arrives five days after the previous beta, with no major new features noted yet.

-

Alibaba's Answer to ChatGPT? Qianwen AI App Launches in Public Beta

Alibaba just launched its Qianwen AI app. We put it head-to-head against ChatGPT in a series of tests to see how this new competitor stacks up.

-

EPOMAKER Launches the TH33, a Feature-Packed Compact Keypad with a Unique Southpaw Layout

EPOMAKER has launched the TH33, a comprehensive keypad featuring a unique left-handed numpad layout, tri-mode connectivity, hot-swappable switches, and QMK/VIA support for full customization.

-

Huawei Mate 70 Air Becomes First Smartphone to Pass UWA's T/UWA 009.3-2-2023 Audio Standard

The newly launched Huawei Mate 70 Air pioneers mobile audio by becoming the first phone to pass the UWA's T/UWA 009.3-2-2023 3D audio standard.

-

Vivo S50 Series Rumored for December Launch with Flagship Snapdragon 8 Gen 5 and Advanced Camera

The vivo S50 series is rumored for a December launch, reportedly featuring a series-wide upgrade including the Snapdragon 8 Gen 5 and an IMX882 periscope camera.

-

AMD's Next-Gen FSR 'Redstone' Debuts, Featuring Ray Regeneration in Call of Duty: Black Ops 7

AMD's new FSR 'Redstone' technology, exclusive to RDNA 4 GPUs, has officially launched, with *Call of Duty: Black Ops 7* being the first game to support its features.

-

Valve Signals Future for Third-Party Steam Machines, Paving the Way for a New Hardware Ecosystem

Valve has signaled that third-party manufacturers may soon release their own SteamOS devices, paving the way for a diverse new ecosystem of Steam Machines with varied hardware.

-

Huawei Mate 80 'Ultra' Rumored to Feature Groundbreaking Dual 50MP Telephoto Camera System

A new leak indicates Huawei's upcoming Mate 80 "ultra" model may feature a groundbreaking physical dual telephoto camera system with two native 50MP sensors.

-

Samsung Launches Galaxy Tab A11+ with 90Hz Display and MediaTek Dimensity 7300 Chip

Samsung introduces the Galaxy Tab A11+, an entry-level tablet with a Dimensity 7300 chip, 11-inch 90Hz screen, and an exceptional promise of seven years of Android updates.

-

Honor 500 Pro Review: A Textbook Mid-Range Phone with Exceptional Feel and Battery Life

The Honor 500 Pro raises the bar for mid-range phones with its stunning design, powerful 200MP camera, marathon 8000mAh battery, and flagship-level performance. A true all-rounder.

-

DJI Osmo Action 6 Review: The New Pinnacle of Action Camera Image Quality?

The DJI Osmo Action 6 sets a new standard with its groundbreaking variable aperture, versatile square sensor, and phenomenal battery life, making it the ultimate tool for action videography.

-

Insta360 X4 Air Review: Making 360 Cameras Accessible and Beginner-Friendly

The Insta360 X4 Air balances 8K quality, portability, and an affordable price, making it the perfect beginner-friendly 360 camera for capturing everything.

-

Nothing Ear 3 Review: Where Striking Design Finally Meets Its Sonic Match

The Nothing Ear 3 stands out with its iconic transparent design and finally delivers a balanced, impressive sound quality, making it a rare blend of style and substance.

-

Redmi K90 Pro Max First Look: Is Game-Changing Audio the Key to Success?

The Redmi K90 Pro Max review: A flagship that stands out with its top-tier performance and a revolutionary BOSE-powered 2.1 sound system, carving a new path.

-

iQOO 15 Review: Perfect Gaming Performance, But Photography Has Its Limits

The iQOO 15 delivers flawless gaming performance with its new Snapdragon chip and 2K 144Hz screen, but its camera capabilities reveal some trade-offs for its gaming-centric design.

-

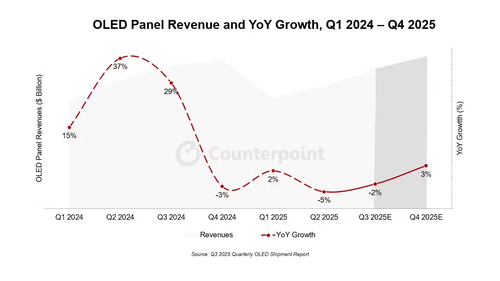

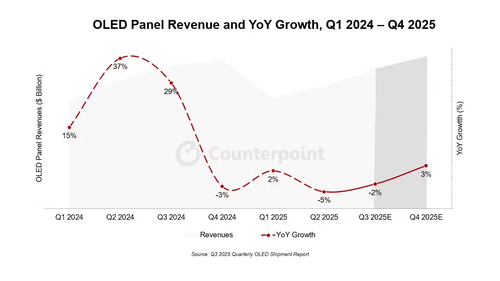

Global OLED Market 2025 Forecast: Samsung Display to Lead with 41% Revenue Share, Says CounterPoint

CounterPoint Research's 2025 OLED market forecast shows Samsung Display leading with 41% revenue share, amidst a market recovery driven by laptops and monitors.

-

The Rise and Swift Fall of the Camera Button: Is Apple's Experiment Over?

Apple's camera button, once hailed as a pro feature and copied by rivals, is rumored to be on its way out. Here’s what went wrong.

-

Report: Nintendo Switch 2 Cartridges to Use 3D NAND for Lower Costs and Higher Capacity

A report from supply chain partner Macronix suggests Nintendo Switch 2 game cartridges will utilize 3D NAND flash, aiming for lower costs and larger storage capacities.

-

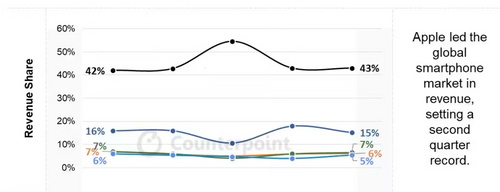

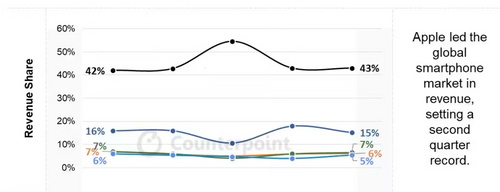

Global Smartphone Market Hits Record $100B in Q2 2025, Apple Dominates Revenue

The global smartphone market reached a record $100 billion in revenue in Q2 2025, with Apple capturing 43% of the total, according to a new Counterpoint Research report.